Jure Repinc

Digital and software freedom/rights advocate from Slovenia, Europe. Also a member of the Pirate party. You can find me on Mastodon: @JRepin@mstdn.io

- 39 Posts

- 2 Comments

Joined 3 years ago

Cake day: June 8th, 2023

You are not logged in. If you use a Fediverse account that is able to follow users, you can follow this user.

6·3 months ago

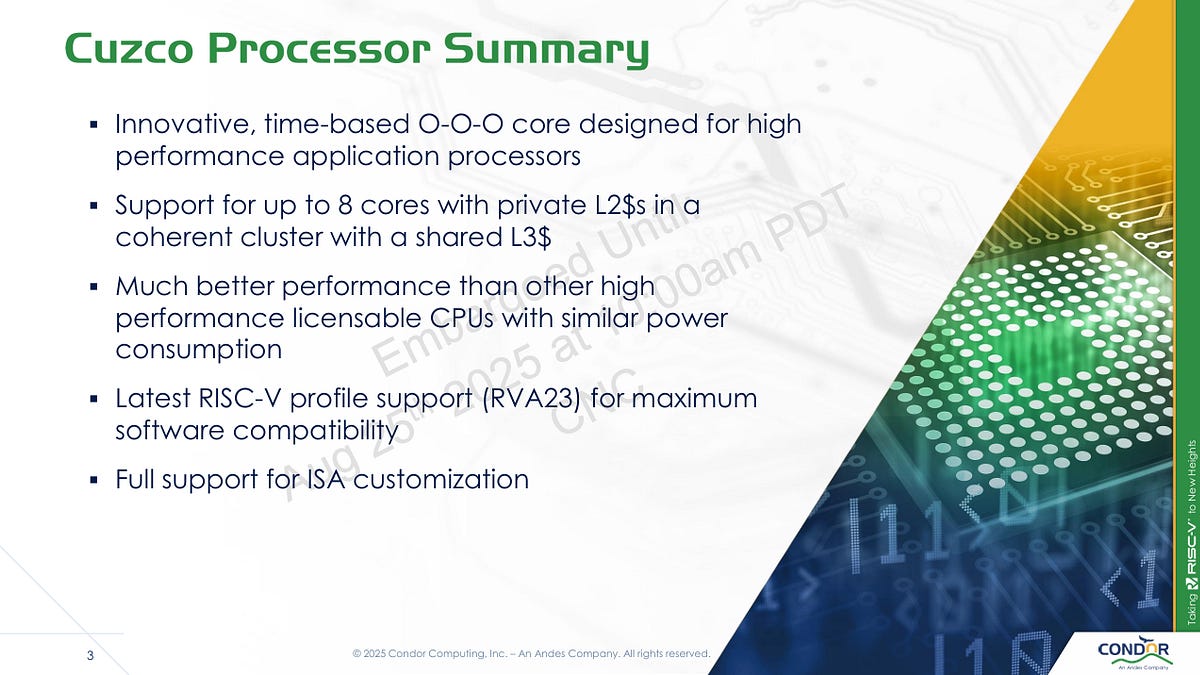

6·3 months agoTo make this easier RISC-V has profiles (the latest being RVA23), which specify a base extension set. So software can target a specific profile, and CPUs advertises which profile they support (+ possible additional extensions). Regarding naming schemes, AMD and Intel are not so clear here either, so it would not be so much different :)

Well for x86 software still needs to be testing if some instructions are supported dynamically if they want to take adventage of the latest ones. For example you still neeed to test for different versions of AVX or even older SSE versions, since not all the x86 CPUs support everything. In 2020 something similar to RISC-V profiles was also defined for x86: microarchitectural levels. And most software just is compiled for the lowest commonly supported set of x86 instructions, in essence x86-64-v1 or x86-64-v2, depends on the software or GNU/Linux distribution. Although recently some distributions started to provide additional higher levels of packages for programs that benefit most from the use of latest x86 instructions. And then glibc HWCAPS feature enables the system to load the most optimized binary of the appliation. For example see openSUSE Tumbleweed gains optional x86-64-v3 optimization.